**SFF-8636**

Specification for

### **Management Interface for 4-lane Modules and Cables**

Rev 2.11 January 03, 2023

SECRETARIAT: SFF TA TWG

This specification is made available for public review at <a href="http://www.snia.org/sff/specifications">http://www.snia.org/sff/specifications</a>. Comments may be submitted at <a href="http://www.snia.org/feedback">http://www.snia.org/feedback</a>. Comments received will be considered for inclusion in future revisions of this specification.

ABSTRACT: This specification defines a common management interface for 4-lane pluggable transceiver modules and cable assemblies. Physical layer and mechanical details of the connector interface are outside the scope of this document.

#### POINTS OF CONTACT:

Vera Koleva Coherent 375 Saxonburg Blvd Saxonburg, PA 16056 vera.koleva@coherent.com Chairman SFF TA TWG Email: <u>SFF-Chair@snia.org</u>

#### **Intellectual Property**

The user's attention is called to the possibility that implementation of this specification may require the use of an invention covered by patent rights. By distribution of this specification, no position is taken with respect to the validity of a claim or claims or of any patent rights in connection therewith.

This specification is considered SNIA Architecture and is covered by the SNIA IP Policy and as a result goes through a request for disclosure when it is published. Additional information can be found at the following locations:

Results of IP Disclosures: http://www.snia.org/sffdisclosures

SNIA IP Policy: <a href="http://www.snia.org/ippolicy">http://www.snia.org/ippolicy</a>

## Copyright

The SNIA hereby grants permission for individuals to use this document for personal use only, and for corporations and other business entities to use this document for internal use only (including internal copying, distribution, and display) provided that:

- 1. Any text, diagram, chart, table or definition reproduced shall be reproduced in its entirety with no alteration, and,

- 2. Any document, printed or electronic, in which material from this document (or any portion hereof) is reproduced shall acknowledge the SNIA copyright on that material, and shall credit the SNIA for granting permission for its reuse.

Other than as explicitly provided above, there may be no commercial use of this document, or sale of any part, or this entire document, or distribution of this document to third parties. All rights not explicitly granted are expressly reserved to SNIA.

Permission to use this document for purposes other than those enumerated (Exception) above may be requested by e-mailing <a href="mailto:copyright\_request@snia.org">copyright\_request@snia.org</a>. Please include the identity of the requesting individual and/or company and a brief description of the purpose, nature, and scope of the requested use. Permission for the Exception shall not be unreasonably withheld. It can be assumed permission is granted if the Exception request is not acknowledged within ten (10) business days of SNIA's receipt. Any denial of permission for the Exception shall include an explanation of such refusal.

### **Disclaimer**

The information contained in this publication is subject to change without notice. The SNIA makes no warranty of any kind with regard to this specification, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The SNIA shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this specification.

Suggestions for revisions should be directed to http://www.snia.org/feedback/.

#### **Foreword**

The development work on this specification was done by the SNIA SFF TWG, an industry group. Since its formation as the SFF Committee in August 1990, the membership has included a mix of companies which are leaders across the industry.

For those who wish to participate in the activities of the SFF TWG, the signup for membership can be found at <a href="http://www.snia.org/sff/join">http://www.snia.org/sff/join</a>.

## **Revision History**

#### **Rev 0.9**

- Clarified wording in 6.2.2

#### **Rev 1.0**

- Added missing reservation entries (Bytes 133, 134, and 220). Modified bit entry labels (Bytes 93 and 136).

#### **Rev 1.2**

- Editorial: Formatted Word controls to improve pagination breaks and comply with style guide.

#### **Rev 1.3**

- Table 20 Identifier Values and Table 24 Encoding Values modified to point to SFF-8024 as the reference for later values and codes.

#### **Rev 1.4**

- Added Revision Compliance Byte. Changed Bytes 1, 131, 138, 146, 164, 188, and 189 to comply with latest SFF-8436 map. Added 12 Gbps SAS bit in Byte 133. Various grammatical changes made.

#### **Rev 1.5**

- Added functionality for QSFP28 (4x25G, 4x28G) transceivers per the requirements of 100GE, EDR InfiniBand and 128GFC Fibre Channel. Tables 7, 8, 10, 12, 13, 17, 19, 20, 21, 23, 29, 29A, 32A, 36, 37, 41 and section 6.2.5, 6.3.6, 6.3.12, 6.3.27.

#### **Rev 1.6**

- Abstract and Scope corrected to include transceiver modules as well as shielded cables as intended applications.

#### Rev 1.7 January 24, 2014

- Editorial: Expanded 2.1 to include specifications referenced in the body. Near-invisible superscripts were modified to be visible text and cross-references made dynamic.

- Reference to SFF-8078 in Table 13 Control Function Bytes corrected to SFF-8079.

- Table 20 Identifier Values and Table 24 Encoding Values which had been retained in the text for information were removed.

- Table 23 Specification Compliance and Table 29A Extended Ethernet Compliance Codes tables were moved to SFF-8024.

#### Rev 1.9 January 27, 2014:

- Clarified Address 5 Loss of Lock indicators as latched

- Added Address 93 bit 2 High Power Class Enable lockout feature

- Clarified Address 98 CDR controls as 1b=On and 0b=Off (i.e. bypassed)

- Clarified Table 21 for Address 129 bits 1-0 to refer to Address 93 bit 2

- Added Adaptive EQ indicator in Address 193 bit 3.

- Clarified Address 194 bits 7-6 setting as 1b=Controllable, 0b=Fixed

- Added Address 220 bit 2 to identify Tx Power diagnostic monitoring supported

- Added Page 03h Address 224 to define magnitude of Tx EQ and Rx Emph supported

- Added Tx Adaptive EQ capability indicator, Page 00h, Address 193 bit 3

- Added Tx Adaptive EQ (per ch) control bits in Page 03h, Address 241 bits 3-0

- Added Tx Adaptive EO Fault flag in Address 6 and masking bits in Address 101

- Added Rx output amplitude support indicators in Page 03h Byte 225

- Added text to section 6.3.2 indicating that the power class identifiers specify worst case maximum power dissipation.

- Added Initialization complete flag to Byte 6 bit 0.

#### Rev 2.0 August 6, 2014:

- Changed the amplitude setting 0 from 200-400 to 100-400mv.

#### **Management Interface for 4-lane Modules and Cables**

- Added Version 2 to address 141.

- Added Version 2 Rate Select table to Table 14 with: 00 as under 12Gb/s, 01 as between 12Gb/s and 24Gb/s, 10 as between 24Gb/s and 26Gb/s and 11 is above 26Gb/s

- Changed revision register compliance bit for revision 1.9 to 2.0 (1.9 was never released)

- Editorial changes to fix spelling and maintain consistent naming.

## Rev 2.1 August 21, 2014:

- Assigned Page 00h Bytes 111-112 for use by PCI-SIG

- Restored Table 23 and Table 24 from SFF-8024

- Replaced 'See SFF-8024 Table 4-x' with 'See SFF-8024 Transceiver Management'

- Made Page/Address Byte, Page/Address, Page/Byte synonyms common: as Page/Byte

- Added Page/Byte/Bit location to those table titles which did not have it

- Alphabetized abbreviations and added some that were missing

- Deleted 'Ethernet' in respect to Extended Specification Compliance Codes

- Replaced Figure 13 with current use of memory

- Other minor corrections e.g. added 'h' as in Page 00h when it was missing

#### **Rev 2.2**

- During the review of Rev 2.1 it was recommended that:

- the contents of Table 22 Connector Type be moved to SFF-8024.

- the contents of Table 24 Encoding Values be returned to SFF-8024.

- Other minor editing improvements

#### **Rev 2.3**

- Nomenclature of 10e in Section 2.5 Abbreviations replaced by 10^

## Rev 2.4 November 7, 2014:

- Adopted Figure/Table numbering style of current template

- To make correlation of previous Change History easier for readers, a Cross Reference of Figures and Tables was prepared.

### Rev 2.5 April 18, 2015:

-Table 6-30 split creating new Table 6-31. Old Tables 6-31 to 6-35 become new Tables 6-32 to 6-36.

Figure 1-1 updated to reference SFF-8665 (QSFP28)

2.1 Industry Documents - added SFF-8665

Table 5-3 updated to include Bytes 93, 98, 99 and 107

Table 5-6 updated to include sub-headings with page numbers and to add Bytes 94-97, 100-104, 105-106, 111-112, 114-118. Changed description of Page 03h Bytes 226-241 to Optional Channel Controls. Added Page 03h Bytes 254-255.

6.1 Overview. Added fourth paragraph explaining details of non-implemented pages.

Figure 6-1. Updated Page 00h descriptions for Bytes 22-33, 100-104, 105-106, 108-110, 111-112, 113 and 114. Removed '(Cable Assemblies)' from Page 03h sub-heading.

6.1.1.1 shortened column descriptions by removing 'applications' from each one.

Table 6-1. Updated descriptions at Bytes 22-33, 86-98, 99, 100-104, 105-106, 108-110, 111-112, 113, 114-118.

6.2.2 Status Indicators. Added text to third sentence of first paragraph to emphasize that both the IntL pin and bit are asserted upon completion of a power up reset.

Table 6-3. Added value 07h for rev 2.5. Added text to value 00h - 'Do not use for...'. Updated value 01h to say SFF-8436 rev 4.8 or earlier.

Table 6-5. Additional description for Byte 6 bit 0 Initialization Complete Flag referencing Table 6-25 for the new Initialization Complete Implemented bit.

6.2.4 Free Side Device Monitors. Added fifth paragraph to explain placement of temperature sensor. Table 6-8. Added Bytes 66-73 description for reserved channel monitor set 5.

Table 6-13. Corrected Byte 101 bits 7-4 names from L-Tx... to M-Tx...

6.2.9 Free Side Device Properties. Added paragraphs 5 and 6 to explain the purpose of Byte 113 bits 3-0 and Byte 113 bits 6-4. This byte is added for breakout cables.

Table 6-14. Added Byte 113 bits 6-4 Far End Implementation and bits 3-0 Near End Implementation descriptions.

6.2.11 Page Select. Added last sentence to define behavior when the host writes an unsupported

#### **Management Interface for 4-lane Modules and Cables**

page value.

Table 6-15. Removed sub-headers for Base ID, Extended ID and Vendor Specific ID Fields. Changed Name of Byte 130 from 'Connector, Media' to 'Connector Type'. Updated description of Byte 146 to clarify that all cable assemblies are in units of 1m and OM4 fiber lengths are in units of 2m.

6.3.8 through 6.3.12. Added words to clarify usage for separable modules and for cable assemblies.

6.3.13. Additional sentence referencing Byte 130 (connector type) to distinguish active optical cable (AOC) from separable module (SM).

Table 6-20. Added '/ Undefined' to value 1000b.

6.3.27 Diagnostic Monitoring Type. Added additional words to fourth and fifth paragraphs to explain the treatment of Byte 220 bits 3-2 when not set.

Table 6-25. Added Byte 221 bit 4 Initialization Complete Flag Implemented, with explanation.

Table 6-29. Reformatted with # Bytes column and updated descriptions.

Table 6-31. Added Byte 225 bits 5-4 Rx output emphasis type with description.

Table 6-32. Bytes 226-233 from Vendor Specific to Reserved. Added descriptions for Byte 241 bits 3-0 to specify that adaptive equalization is the default if it is implemented.

Table 6-35. Code 1xxx from Vendor Specific to Reserved.

6.6.2 Optional Channel Controls. Added 2 sentences at the end of first paragraph to explain that free side devices can limit the maximum emphasis supported using Byte 224.

#### Rev 2.6 June 19, 2015:

Title changed per request to comply with the lexicon

Table 5-4 and other content consolidated into Table 5-3.

#### Rev 2.7 January 26, 2016:

Updates as per "bucket list" comment resolution.

Editorial corrections throughout.

Added SAS 24.0 Gbps bit in Table 6-17.

## Rev 2.9 April 21, 2017:

Published version incorporating editorial comments received during approval ballot.

Cover Page: added David Lewis to Points of Contact.

Expressions of Support by Manufacturers: Removed names pending new ballot.

Cross Reference of Figures and Tables: Added new Table 6-10 and incremented all Table numbers from 6-11 to 6-37

2.1 Industry Documents: added SFF-8436, INF-8438, SFF-8679.

Figure 6-1 Common Memory Map: changed description of bytes 100-104 to match other places in the document.

Table 6-2 Status Indicators: Byte 2, bits 7-4 now reserved for microQSFP MSA module state field. Improved descriptions for byte 2 bits 1-0.

Table 6-3 Revision Compliance: Added 08h for SFF-8636 Rev 2.8.

Table 6-5 Free Side Monitor Interrupt Flags: Added byte 6, bit 1 for TEC readiness flag.

Table 6-9 Control Function Bytes: New descriptions for Byte 93, bit 2-0.

6.2.6 Control Functions: 4 new paragraphs describing power levels and related control functions. New Table 6-10 Truth Table for Enabling Power Classes. All following table numbers increased by

6.2.7.2 Extended Rate Selection: Modified first sentence to clarify that page 00h, byte 195 bit 5 needs to be set for rate selection to be supported.

Table 6-14 Hardware Interrupt Pin Masking Bits: Added byte 103, bit 1 for TEC readiness flag masking bit.

Table 6-15 Free-Side Device Properties: Byte 114 removed from reserved and assigned for microQSFP MSA maximum duration fields.

Table 6-16 Upper Page 00h Memory Map: Added definition to byte 142 Length (SMF) to say that a value of 1 shall be used for reaches from 0 to 1 km. Added a new use for byte 145 Length (OM1 62.5 um) or Copper Cable Attenuation. Corrected byte 189 copper cable attenuation frequency from 12 to 12.9 GHz.

Table 6-19 Extended Rate Select Compliance Tag Assignment: Modified description of byte 141 bits 1-0.

6.3.11 Length (OM1) or Copper Cable Attenuation: Added new paragraph describing support for

copper cable assemblies.

Table 6-22 Extended Module Code Values: Added byte 164 bit 5 for HDR module code.

6.3.20: corrected section title to Wavelength Tolerance or Copper Cable Attenuation.

Table 6-23 Option Values: Byte 195 bit 0 used to indicate support for pages 20h-21h. voltage monitoring.

Table 6-26 Enhanced Options: Added byte 221 bit 1 for TEC readiness flag implemented.

6.6 Upper page 03h: first paragraph modified to say that page 03h includes ability registers for optional equalizer, emphasis and amplitude.

6.6.1 Free-Side Device and Channel Thresholds: Added paragraph after Table 6-31.

Table 6-33 Optional Channel Controls: Added byte 228 Maximum TEC stabilization time and byte 229 Maximum CTLE settling time. Improved descriptions for bytes 238-239 Rx Output Amplitude Controls.

6.6.3 Optional Channel Controls: Added paragraph after Table 6-36 to clarify that Rx amplitude and emphasis are measured at the relevant test point.

Added new section 6.7 for Tables 20h-21h.

Added Annex A – alternative text for section 6.2.7 Rate Select and Configuration for Multi-Rate Modules.

Table 5-3 Added pages 20-21h

Figure 6-1 Replaced with new figure that includes pages 20-21h

Table 6-2 Replaced (O) with (-) in byte 2 bits 7-4

Table 6-2 Removed (if pin supported) from description of IntL bit

Table 6-2 Made the IntL bit (R) for all free side devices

Table 6-5 Updated the description of TC readiness flag to reflect correct reassert behavior

6.2.4 Removed reference to an external temperature control location

Table 6-9 Changed all entries from (O) to (-) for PC free side device

Table 6-15 Updated descriptions of Advanced Low Power bits and Min. Operating Voltage bits

Table 6-15 Provided names of PCI SIG specifications that use bytes 111-112

Table 6-16 Updated descriptions of bytes 142-146 to say that the link lengths apply at the stated bit rate

Table 6-23 Changed byte 193 bit 4 from reserved to "Tx Input Adaptive Equalizer Freeze Capable" bit.

Table 6-32 Moved Max. TC Stabilization Time and Max. CTLE Settling Time bytes from Table 6-33 to end of Table 6-32. Added units to descriptions. Changed table title to include timing.

Table 6-33 Changed byte 233 bits 4-0 from reserved to Tx Adaptive Equalizer Freeze control bits.

Section 6.7 Reorganization and rewording throughout.

Editorial changes for bucket list items that were missed in rev 2.8.2

#### **Rev 2.10 September 18, 2019:**

**Deprecated Table 01h** and associated advertising and control bits for "Application Select Table per SFF-8079". This feature is considered obsolete.

Bytes 89-92 and 94-97 now reserved (were controls for SFF-8079).

Advertising bit at Page 00h, Byte 221, bit 2, is now reserved.

Added **SW reset** control at byte 93, bit 7 and advertising bit at Page 00h, Byte 221, bit 0.

Added support for **power class 8** as described in SFF-8679 including:

Control for High Power Class 8 at byte 93, bit 3.

Advertising Max Power Consumption at byte 107.

Added support for **reconfiguration of LPMode/TxDis and IntL/RxLOSL** dual-purpose signals as described in SFF-8679.

Controls for reconfiguration at byte 99, bits 1-0.

Advertising bits at Page 00h, Byte 193, bits 6-5.

Added **ModSelL wait time** advertising field (byte 116) and text description at section 6.2.9.

Added a **Secondary Extended Spec Compliance Code** byte (byte 116).

Reworded description of bytes 140 and Page 00h, byte 222 from "BR, nominal" to "Signaling rate, nominal" and changed units from Mb/s to MBd.

Added advertising and controls for optional Controllable Host-side FEC support, and

**Controllable Media-side FEC** support for modules with FEC inside the module. Advertising bits at Page 03h, byte 227, bits 7-6. Controls at Page 03h, byte 230, bits 7-6.

Added controls for per-lane **Tx forced squelch** at Page 03h, byte 231, bits 3-0 and an advertising bit at Page 03h, byte 227, bit 3.

Added advertising bits for **Fast RxLOS and Fast TxDis** capabilities as specified in SFF-8679. Page 03h, byte 227, bits 2-1.

**Updated list of industry documents** at 2.1 and added a note to say that SFF-8431 is archived and is replaced by SFF-8418 and SFF-8419.

Improved description of byte 2, bit 2 in Table 6-2.

**Added notes to Table 6-13** referring the reader to SFF-8449 for SAS applications.

Editorial improvements throughout.

## Rev 2.10a September 24, 2019:

Removed "draft" from cover page of published document.

## Rev 2.11 January 03, 2023:

Replaced master/slave with controller/target throughout the document.

Added Transceiver Subtype code and Fiber Face type code Page 00h, byte 117.

Re-labeled Figure 6-1 as Table 6-1 and renumbered consecutive tables and figures

Replaced master/slave with controller/target in figures 5-1 through 5-6. Replaced the tables with editable format (were images)

Moved byte 117 from Reserved to Free Side Device Properties group in Table 6-1 and Table 5-3 Added text describing the new fields in register 117.

Several editorial changes

To avoid confusion for PAM4 based transceivers, replaced "bit rate" with "signaling rate "or "rate" To avoid confusion with information transfer rate, data rate, and signaling rate changed "data rate" to "rate "in few places in Appendix A.

## **Contents**

| 1 | Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13                                                                              |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 2 | References and Conventions 2.1 Industry Documents 2.2 Sources 2.3 Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13<br>13<br>13<br>13                                                            |

| 3 | Keywords, Acronyms, and Definitions 3.1 Keywords 3.2 Acronyms and Abbreviations 3.3 Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15<br>15<br>16<br>17                                                            |

| 4 | General Description 4.1 Fixed-to-Free Side Block Diagram 4.2 Signal Definition 4.2.1 SCL 4.2.2 SDA 4.2.3 Other Signals 4.3 Physical Implementation 4.3.1 Cable Assembly 4.3.2 Separable Transceiver Modules 4.3.3 Management Interface Scope 4.4 Reset Behavior 4.4.1 Protocol Reset 4.4.2 Power On Reset 4.4.3 Reset Signals                                                                                                                                                                                                                                                                                                                                                                       | 18<br>18<br>19<br>19<br>19<br>19<br>19<br>20<br>21<br>21<br>21                  |

| 5 | 2-wire Bus Interface 5.1 Signal Interface 5.2 2-wire Bus Protocol 5.2.1 The operational States and State Transitions 5.2.1.1 Start 5.2.1.2 Stop 5.2.1.3 Acknowledge 5.2.1.4 Clock Stretching 5.2.2 Protocol Reset 5.2.3 Format 5.2.3.1 Control 5.2.3.2 Address and Data 5.3 Read/Write Operations 5.3.1 Target Memory Address Counter (Read and Write Operations) 5.3.2 Write Operations (BYTE Write) 5.3.3 Write Operations (Sequential Write) 5.3.4 Write Operations (Acknowledge Polling) 5.3.5 Read Operations (Current Address Read) 5.3.6 Read Operations (Random Read) 5.3.7 Read Operations (Sequential Read) 5.4.1 Timing Diagram 5.4.2 Timing Parameters 5.5 Write Operation Restrictions | 21<br>21<br>21<br>21<br>21<br>21<br>21<br>22<br>22<br>22<br>22<br>22<br>22<br>2 |

| 6 | Memory Map 6.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28<br>28                                                                        |

|        | Required Versus Optional Functionality                                                                                                           | 30       |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 6.2 Lo | wer Page 00h                                                                                                                                     | 31       |

| 6.2.1  | Identifier                                                                                                                                       | 31       |

| 6.2.2  | Status Indicators (Page 00h, Bytes 1-2)                                                                                                          | 31       |

| 6.2.3  | Interrupt Flags (Page 00h, Bytes 3-21)                                                                                                           | 32       |

|        | Free Side Device Monitors (Page 00h, Bytes 22-33)                                                                                                | 35       |

|        | Channel Monitors (Page 00h, Bytes 34-81)                                                                                                         | 35       |

|        | Control Functions (Page 00h, Bytes 86-99)                                                                                                        | 37       |

|        | Rate Select                                                                                                                                      | 39       |

| 6.2.7  |                                                                                                                                                  | 39       |

|        | 7.2 Extended Rate Selection                                                                                                                      | 40       |

|        | Free Side Device Indicators and Channel Masks (Page 00h, Bytes 100-106)                                                                          | 41       |

| 6.2.9  | ` • · · · · · · · · · · · · · · · · · ·                                                                                                          | 43       |

|        | , , , , , , , , , , , , , , , , , , , ,                                                                                                          | 45       |

| 6.2.11 | Password Entry and Change (Page 00h, Bytes 119-126)                                                                                              | 45       |

|        |                                                                                                                                                  |          |

|        | per Page 00h                                                                                                                                     | 46       |

|        | Identifier (00h 128)                                                                                                                             | 48       |

|        | Extended Identifier (00h 129)                                                                                                                    | 48       |

|        | Connector Type (00h 130)                                                                                                                         | 48       |

|        | Specification Compliance (00h 131-138)                                                                                                           | 49       |

|        | Encoding (00h 139)                                                                                                                               | 50       |

| 6.3.6  | Nominal Signaling Rate (00h 140)                                                                                                                 | 50       |

|        | Extended Rate Select Compliance (00h 141)                                                                                                        | 50       |

| 6.3.8  | Length (Standard SM Fiber) -km (00h 142)                                                                                                         | 50       |

|        | Length (OM3) (00h 143)                                                                                                                           | 51       |

|        | Length (OM2) (00h 144)                                                                                                                           | 51       |

|        | Length (OM1) or Copper Cable Attenuation (00h 145)                                                                                               | 51       |

| 6.3.12 |                                                                                                                                                  | 51       |

| 6.3.13 |                                                                                                                                                  | 51       |

| 6.3.14 | Vendor Name (00h 148-163)                                                                                                                        | 52       |

| 6.3.15 | Extended Module Codes (00h 164)                                                                                                                  | 52       |

| 6.3.16 | Vendor Organizationally Unique Identifier Field (00h 165-167)                                                                                    | 53       |

| 6.3.17 | Vendor Part Number (00h 168-183)                                                                                                                 | 53       |

| 6.3.18 | Vendor Revision Number (00h 184-185)                                                                                                             | 53       |

| 6.3.19 | Wavelength or Copper Cable Attenuation (00h 186-187)                                                                                             | 53       |

| 6.3.20 |                                                                                                                                                  | 53       |

| 6.3.21 |                                                                                                                                                  | 54       |

|        | CC_BASE (00h 191)                                                                                                                                | 54       |

| 6.3.23 |                                                                                                                                                  | 54       |

| 6.3.24 |                                                                                                                                                  | 54       |

| 6.3.25 |                                                                                                                                                  | 55       |

| 6.3.26 | · · · · · · · · · · · · · · · · · · ·                                                                                                            | 55       |

| 6.3.27 | · · ·                                                                                                                                            | 56       |

| 6.3.28 |                                                                                                                                                  | 57       |

| 6.3.29 | , ,                                                                                                                                              | 57<br>57 |

|        | Vendor Specific (00h 224-255)                                                                                                                    | 57<br>57 |

|        | per Page 01h (Optional)                                                                                                                          | 58       |

|        | per Page 02h (Optional)                                                                                                                          | 58       |

|        | per Page 03h (Optional)                                                                                                                          | 59       |

|        |                                                                                                                                                  | 59<br>59 |

| 6.6.1  | Free Side Device and Channel Thresholds (Page 03h, Bytes 128-223) Optional Equalizer Emphasis and Amplitude Indicators (Page 03h, Bytes 224 230) |          |

|        | Optional Equalizer, Emphasis and Amplitude Indicators (Page 03h, Bytes 224-229)                                                                  | 61       |

|        | Optional Channel Controls (Page 03h, Bytes 230-241)                                                                                              | 62       |

|        | Channel Monitor Masks (Page 03h, Bytes 242-251)                                                                                                  | 65<br>67 |

|        | per Page 20h and Upper Page 21h (Optional)                                                                                                       | 67       |

| 6.7.1  | Overview                                                                                                                                         | 67       |

|   | 6.7.2 Registers for Page 20h     | n and 21h                                        | 68 |

|---|----------------------------------|--------------------------------------------------|----|

|   | 6.7.2.1 Overview                 |                                                  | 68 |

|   | 6.7.2.2 Latched Alarm/Wa         | rning Flags for Monitored Parameters             | 68 |

|   | 6.7.2.3 Mask Registers for       | Monitored Parameters                             | 69 |

|   | 6.7.2.4 Real-Time Value of       | f Monitored Parameters                           | 70 |

|   | 6.7.2.5 Parameter Configu        | ration Registers                                 | 72 |

|   | 6.7.2.6 Electrical/Optical La    | ane Mapping                                      | 75 |

|   | 6.7.2.7 Other Configuration      | n Registers                                      | 76 |

|   | 6.7.2.8 Threshold Register       |                                                  | 77 |

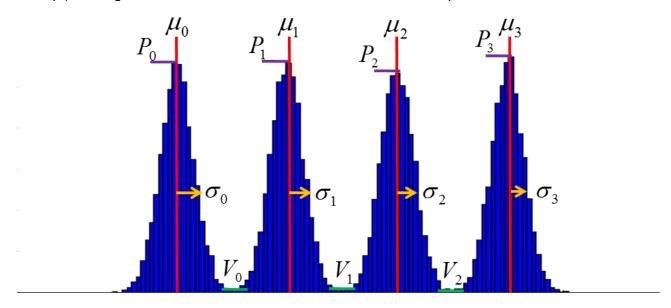

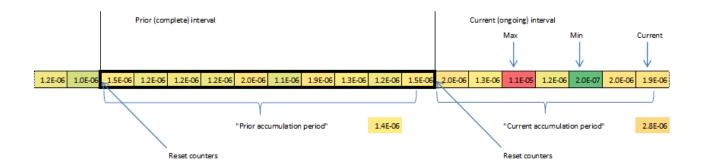

|   | 6.7.3 Diagrams for PAM4 Mo       | onitored Parameters                              | 77 |

|   | 6.7.4 Detailed Description of    | f New Monitored Parameters for PAM4              | 79 |

|   | 6.7.4.1 SNR                      |                                                  | 79 |

|   | 6.7.4.2 Residual ISI/Disper      | rsion:                                           | 79 |

|   | 6.7.4.3 PAM Level Transition     | on Parameter                                     | 79 |

|   | 6.7.4.4 Error Figures            |                                                  | 79 |

|   | •                                | f New Monitored Parameters for DWDM              | 81 |

|   | 6.7.5.1 TC Current               |                                                  | 81 |

|   | 6.7.5.2 Laser Frequency          |                                                  | 81 |

|   | 6.7.5.3 Laser Temperature        |                                                  | 81 |

| Α | Appendix A. Rate Select and Co   | nfiguration for Multi-rate Modules (Informative) | 82 |

|   | A.1 Direct Control Configuration | on                                               | 82 |

|   | A.2 Rate Select                  |                                                  | 83 |

|   | A.3 Extended Rate Selection      |                                                  | 83 |

| Figures    |                                                                                                                              |                  |

|------------|------------------------------------------------------------------------------------------------------------------------------|------------------|

| Figure 3-1 | Bit Organization                                                                                                             | 17               |

| Figure 4-1 | Common Management Interface Block Diagram                                                                                    | 18               |

|            | Cable Assembly Implementation                                                                                                | 19               |

|            | Separable Transceiver Module Implementation                                                                                  | 20               |

| _          | Management Interface Scope                                                                                                   | 20               |

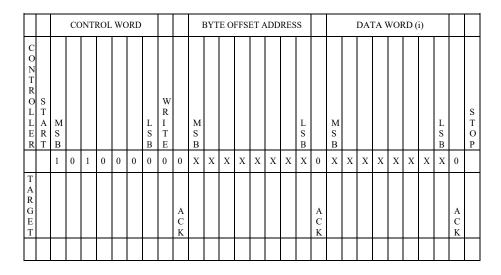

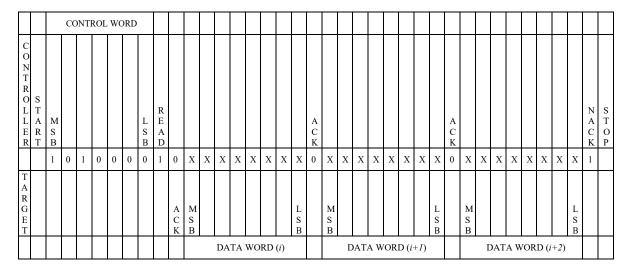

| Figure 5-1 | Write Byte Operation                                                                                                         | 23               |

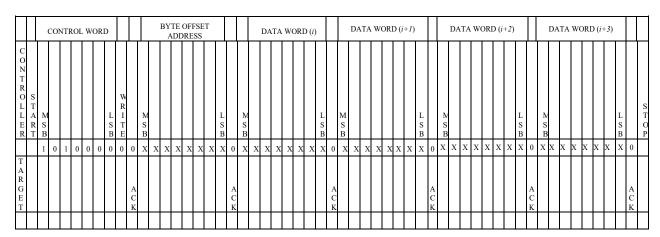

| Figure 5-2 | Sequential Write Operation                                                                                                   | 23               |

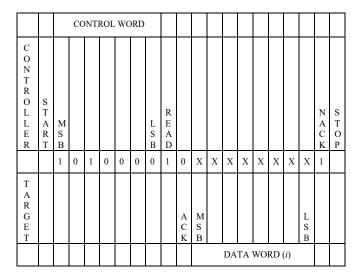

| Figure 5-3 | Current Address Read                                                                                                         | 24               |

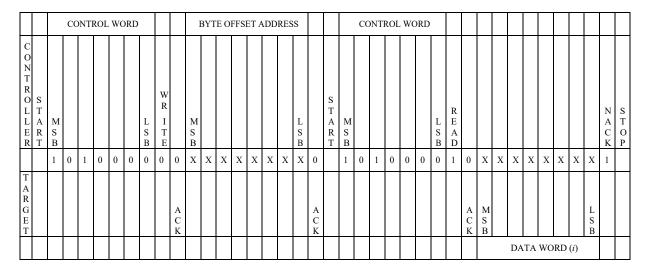

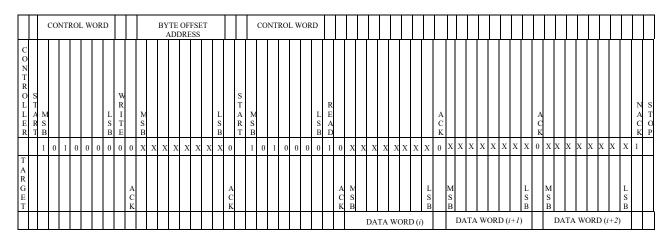

| -          | Random Read                                                                                                                  | 24               |

| •          | Sequential Address Read Starting at Current Address                                                                          | 25               |

|            | Sequential Address Read Starting with Random Read                                                                            | 25               |

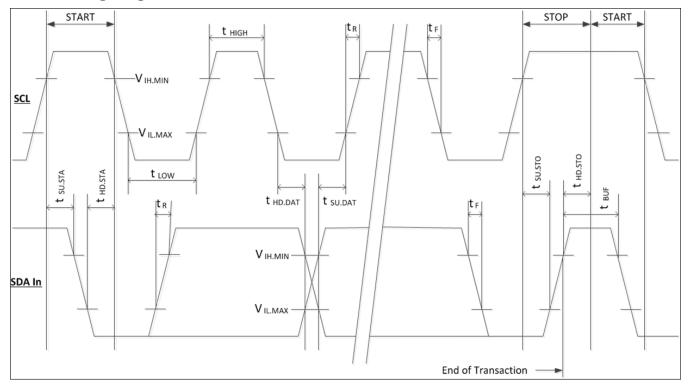

| -          | Timing Diagram                                                                                                               | 26               |

|            | Optical ingress path of Module                                                                                               | 78               |

|            | PAM4 vertical slice histogram                                                                                                | 78               |

| Figure 6-3 | Error rate accumulation intervals                                                                                            | 80               |

| Tables     |                                                                                                                              |                  |

| Table 5-1  | Management Interface timing parameters                                                                                       | 26               |

|            | Non-Volatile Memory Specification                                                                                            | 27               |

|            | Nritable Memory Blocks                                                                                                       | 27               |

|            | Common Memory Map                                                                                                            | 29               |

|            | Lower Page 00h Memory Map                                                                                                    | 31               |

|            | Status Indicators (Page 00h Bytes 1-2)                                                                                       | 31               |

|            | Revision Compliance (Page 00h Byte 1)                                                                                        | 32               |

|            | Channel Status Interrupt Flags (Page 00h Bytes 3-5)                                                                          | 33               |

|            | Free Side Monitor Interrupt Flags (Page 00h Bytes 6-8)                                                                       | 33               |

|            | Channel Monitor Interrupt Flags (Page 00h Bytes 9-21)                                                                        | 34               |

|            | Free Side Monitoring Values (Page 00h Bytes 22-33)                                                                           | 35               |

|            | Channel Monitoring Values (Page 00h Bytes 34-81)                                                                             | 36               |

|            | Control Function Bytes (Page 00h Bytes 86-99)                                                                                | 37               |

|            | Truth table for enabling power classes (Page 00h Byte 93)                                                                    | 39               |

|            | xN_Rate_Select with Extended Rate Selection                                                                                  | 4(               |

|            | Hardware Interrupt Pin Masking Bits (Page 00h Bytes 100-106)                                                                 | 41               |

|            | Free Side Device Properties (Page 00h Bytes 107-116)                                                                         | 44<br>46         |

|            | Upper Page 00h Memory Map                                                                                                    | 48               |

|            | Extended Identifier Values (Page 00h Byte 129)                                                                               |                  |

|            | Specification Compliance Codes (Page 00h Bytes 131-138)  Extended Rate Select Compliance Tag Assignment (Page 00h Bytes 141) | 4 <u>9</u><br>50 |

|            | Extended Rate Select Compliance Tag Assignment (Page 00h Byte 141)<br>Device Technology (Page 00h Byte 147)                  | 52               |

|            | Transmitter Technology (Page 00h Byte 147)                                                                                   | 52               |

|            | Extended Module Code Values (Page 00h Byte 164)                                                                              | 52               |

|            | Option Values (Page 00h Bytes 193-195)                                                                                       | 55               |

|            | Date Codes (Page 00h Bytes 212-219)                                                                                          | 55               |

|            | Diagnostic Monitoring Type (Page 00h Byte 220)                                                                               | 56               |

|            | Enhanced Options (Page 00h Byte 221)                                                                                         | 57               |

|            | Extended Baud Rate: Nominal (Page 00h Byte 222)                                                                              | 57               |

|            | Upper Page 03h Memory Map                                                                                                    | 59               |

|            | Free Side Device and Channel Thresholds (Page 03h Bytes 128-223)                                                             | 59               |

|            | Equalizer, Emphasis, Amplitude and Timing (Page 03h Bytes 224-229)                                                           | 61               |

|            | Optional Channel Controls (Page 03h Bytes 230-241)                                                                           | 62               |

|            | Output Differential Amplitude Control (Page 03h Bytes 238-239)                                                               | 63               |

|            | Tx Input Equalizer Controls (Page 03h Bytes 234-235)                                                                         | 63               |

|            | Rx Output Emphasis Controls (Page 03h Bytes 236-237)                                                                         | 64               |

|            |                                                                                                                              | _                |

| Tx Squelch Truth Table                                     | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel Monitor Masks (Page 03h Bytes 242-251)             | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Register overview for page 20h                             | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Register overview for page 21h                             | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Latched Alarm/Warning Flags (Page 20h Bytes 128-139)       | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Interrupt Mask Registers (Page 20h Bytes 140-151)          | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Real-Time Value Registers (Page 20h Bytes 152-199)         | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Parameter Configuration Registers (Page 20h Bytes 200-247) | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Parameter Configuration Details                            | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Parameter Type Enumeration                                 | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Lane Mapping Registers (Table 20h Bytes 248-249)           | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Lane Mapping Enumeration                                   | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Other Configuration Registers (Table 20h Bytes 250-255)    | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Threshold Registers (Page 21h Bytes 128-255)               | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Encoding for BER/FER                                       | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Rate Select Advertising Bits                               | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| XN_Rate_Select with Extended Rate Selection                | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                            | Channel Monitor Masks (Page 03h Bytes 242-251) Register overview for page 20h Register overview for page 21h Latched Alarm/Warning Flags (Page 20h Bytes 128-139) Interrupt Mask Registers (Page 20h Bytes 140-151) Real-Time Value Registers (Page 20h Bytes 152-199) Parameter Configuration Registers (Page 20h Bytes 200-247) Parameter Configuration Details Parameter Type Enumeration Lane Mapping Registers (Table 20h Bytes 248-249) Lane Mapping Enumeration Other Configuration Registers (Table 20h Bytes 250-255) Threshold Registers (Page 21h Bytes 128-255) Encoding for BER/FER Rate Select Advertising Bits |

# 1 Scope

This specification defines a common memory map and protocol that can be used to manage both 4-channel pluggable transceiver modules and 4-channel managed external cable interface implementations. Physical layer and mechanical details of the interface are outside the scope of this document. Memory map details and communication protocol used to transfer the information are described within this document. This approach facilitates a common memory map and management interface for modules or cable assemblies with different mechanical, physical layer, and other characteristics. Examples include the QSFP+ family and mini multilane connectors for SAS (see REF-TA-1011).

This specification does not apply to the CFP MSA family of modules, which use the MDIO interface and a different memory map.

# 2 References and Conventions

# 2.1 Industry Documents

The following documents are relevant to this specification:

| - INF-8074    | SFP (Small Formfactor Pluggable) Transceiver                                                  |

|---------------|-----------------------------------------------------------------------------------------------|

| - INF-8438    | QSFP (Quad Small Formfactor Pluggable) Transceiver                                            |

| - REF-TA-1011 | Cross Reference to Select SFF Connectors and Modules                                          |

| - SFF-8024    | SFF Module Management Reference Code Tables                                                   |

| - SFF-8079    | SFP Rate and Application Selection                                                            |

| - SFF-8418    | SFP+ 10 Gb/s Electrical Interface                                                             |

| - SFF-8419    | SFP+ Power and Low Speed Interface                                                            |

| - SFF-8431    | SFP+ 10 Gb/s and Low Speed Electrical Interface [Archived, replaced by SFF-8418 and SFF-8419] |

| - SFF-8436    | QSFP+ 10 Gbs 4X Pluggable Transceiver                                                         |

| - SFF-8449    | Management Interface for SAS Shielded Cables                                                  |

| - SFF-8472    | Management Interface for SFP+                                                                 |

| - SFF-8665    | QSFP+ 28 Gb/s 4X Pluggable Transceiver Solution (QSFP28)                                      |

| - SFF-8679    | QSFP+ 4X Hardware and Electrical Specification                                                |

## 2.2 Sources

The complete list of SFF documents which have been published are currently being worked on, or that have been expired by the SFF Committee can be found at <a href="http://www.snia.org/sff/specifications">http://www.snia.org/sff/specifications</a>. Suggestions for improvement of this specification will be welcome, they should be submitted to <a href="http://www.snia.org/feedback">http://www.snia.org/feedback</a>.

### 2.3 Conventions

The following conventions are used throughout this document:

#### **DEFINITIONS**

Certain words and terms used in this standard have a specific meaning beyond the normal English meaning. These words and terms are defined either in the definitions or in the text where they first appear.

#### **ORDER OF PRECEDENCE**

If a conflict arises between text, tables, or figures, the order of precedence to resolve the conflicts is text; then tables; and finally figures. Not all tables or figures are fully described in the text. Tables show data format and values.

#### **NUMBERING CONVENTIONS**

The ISO convention of numbering is used (i.e., the thousands and higher multiples are separated by a space and a period is used as the decimal point). This is equivalent to the English/American convention of a comma and a period.

| American    | French      | ISO         |

|-------------|-------------|-------------|

| 0.6         | 0,6         | 0.6         |

| 1,000       | 1 000       | 1 000       |

| 1,323,462.9 | 1 323 462,9 | 1 323 462.9 |

#### **NUMERALS CONSTANTS**

Numerals without suffix are understood as numbers in decimal notation (e.g. 16). Hexadecimal literals are marked with a suffix 'h' (e.g. 10h), often written with leading zeroes (0010h). Binary literals are marked with a suffix 'b' (e.g. 10000b), often written with leading zeroes (00010000b). The suffixes may be omitted for unambiguous cases like 0=0b=0h and 1=1b=1h. Spaces may be inserted to make long hexadecimal or binary digit strings readable (e.g. 0001 0000b).

# 3 Keywords, Acronyms, and Definitions

For the purposes of this document, the following keywords, acronyms, and definitions apply.

# 3.1 Keywords

May/ may not: Indicates flexibility of choice with no implied preference.

**Obsolete:** Indicates that an item was defined in prior specifications but has been removed from this specification.

**Optional:** Describes features which are not required by the SFF specification. However, if any feature defined by the SFF specification is implemented, it shall be done in the same way as defined by the specification. Describing a feature as optional in the text is done to assist the reader.

**Reserved:** Defines the signal on a connector contact [when] its actual function is set aside for future standardization. It is not available for vendor-specific use. Where this term is used for bits, bytes, fields, and values; the bits, bytes, fields, and values are set aside for future standardization. The default value shall be zero. The originator is required to define a Reserved field or bit as zero, but the receiver should not check Reserved fields or bits for zero.

**Shall:** Indicates a mandatory requirement. Designers are required to implement all such mandatory requirements to ensure interoperability with other products that conform to this specification.

**Should:** Indicates flexibility of choice with a strongly preferred alternative.

**Vendor specific:** Indicates something (e.g., a bit, field, code value) that is not defined by this specification. Specification of the referenced item is determined by the manufacturer and may be used differently in various implementations.

# 3.2 Acronyms and Abbreviations

AC active cable

AO active optical cable

b binary (suffix to preceding binary based number)

oC degrees Celsius (thermal unit associated with a value)

c conditional upon another parameter which is optional

CDR clock and data recovery

dB decibel (base 10 logarithmic unit) dBm decibels above one milliwatt

Gbps gigabits per second (i.e., 10<sup>9</sup> bits per second)

GHz gigahertz (i.e., 10<sup>9</sup> cycles per second)

h hexadecimal (suffix to preceding hexadecimal based number)

Hz hertz (i.e., cycles per second)

kHz kilohertz (i.e., 10<sup>3</sup> cycles per second)

km kilometer (i.e., 10<sup>3</sup> meters)

LSB least significant bit m meter (unit of length)

mA milliampere (i.e., 10^-3 amperes)

Mbps megabits per second (i.e., 10<sup>6</sup> bits per second)

MHz megahertz (i.e., 10<sup>6</sup> cycles per second)

ms millisecond (i.e., 10^-3 seconds)

MSB most significant bit

mV millivolt (i.e., 10^-3 volts)

mW milliwatt (i.e., 10^-3 watts)

nm nanometer (i.e., 10^-9 meters)

ns nanosecond (i.e., 10^-9 seconds)

O optional P-P peak-to-peak

PAM4 four-level pulse amplitude modulation

PC passive cable

ps picosecond (i.e., 10^-12 seconds)

R required Rx receiver

s second (unit of time) SM separable module

TC temperature controller (e.g. thermo-electric cooler)

Tx transmitter

μA microampere (i.e., 10^-6 amperes)

μm micrometer (i.e., 10^-6 meters)

μs microsecond (i.e., 10^-6 seconds)

μV microvolt (i.e., 10^-6 volts)

μW microwatt (i.e., 10^-6 watts)

V volt (unit of electrical potential)

W watt (unit of electrical power)

#### 3.3 Definitions

### **Bit Organization**

8-bit fields have the most significant bit at bit 7, and 16-bit fields have the most significant bit at bit 15. See Figure 3-1.

|     |    |    |    |    |    |    |         | MSB  |   |   | 8-bit F | ield |   |   | LSB |

|-----|----|----|----|----|----|----|---------|------|---|---|---------|------|---|---|-----|

| MSB |    |    |    |    |    | 10 | 6-bit F | ield |   |   |         |      |   |   | LSB |

| 15  | 14 | 13 | 12 | 11 | 10 | 9  | 8       | 7    | 6 | 5 | 4       | 3    | 2 | 1 | 0   |

Figure 3-1 Bit Organization

#### **Fixed**

The terminology "fixed" is used to describe the gender of the mating side of the connector that accepts its mate upon mating. This gender is frequently, but not always, associated with the common terminology "receptacle". Other terms commonly used are "female" and "socket connector". The term "fixed" is adopted from EIA standard terminology as the gender that most commonly exists on the fixed end of a connection, for example, on the board or bulkhead side. In this document, the terms "fixed", "fixed-side", and "host" are equivalent.

#### **Free**

The terminology "free" is used to describe the gender of the mating side of the connector that penetrates its mate upon mating. This gender is frequently, but not always, associated with the common terminology "plug". Other terms commonly used are "male" and "pin connector". The term "free" is adopted from EIA standard terminology as the gender that most commonly exists on the free end of a connection, for example, on the cable side. In this document, the terms "free", "free-side", and "module" are equivalent.

#### **Passive Cable**

In this specification, a passive cable requires power only to operate the management interface circuitry.

### **Active Cable**

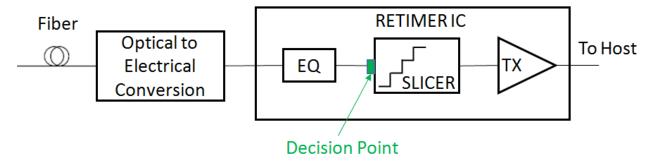

In this specification, an active cable requires power for circuitry that is used to transmit and receive high-speed signals. In addition, power is required to operate the management interface. The high-speed electrical interface of the cable may contain equalizers and retimers (CDRs) which are managed by registers defined in this management interface specification.

#### **Pluggable Transceiver Module**

In this specification, a pluggable transceiver module, also known as a separable module (SM), requires power for the management interface and for the circuitry integral to the Tx/Rx high-speed serial channels supported by the module. The module also has a media dependent interface (MDI), such as a duplex single mode fiber or a parallel multimode fiber connector. The high-speed electrical interface of the module may contain equalizers and retimers (CDRs) which are managed by registers defined in this management interface specification. In this document, the terms "free", "free-side", and "module" are equivalent.

# 4 General Description

The management interface provides a method for the fixed side to determine the characteristics and status of the free side through a memory map. In some implementations, the interface also provides a mechanism to control the operation of the free side circuitry. For the case where the module is an end of a cable assembly, the host can determine if the cable assembly is passive, active copper, or active optical. For the case where the module is a transceiver, the host can determine if the module is used with single-mode or multimode fiber, or a copper cable assembly, and which industry standards are supported. Parameters such as supplier, part number, propagation delay and loss (for passive cable assemblies) can also be determined.

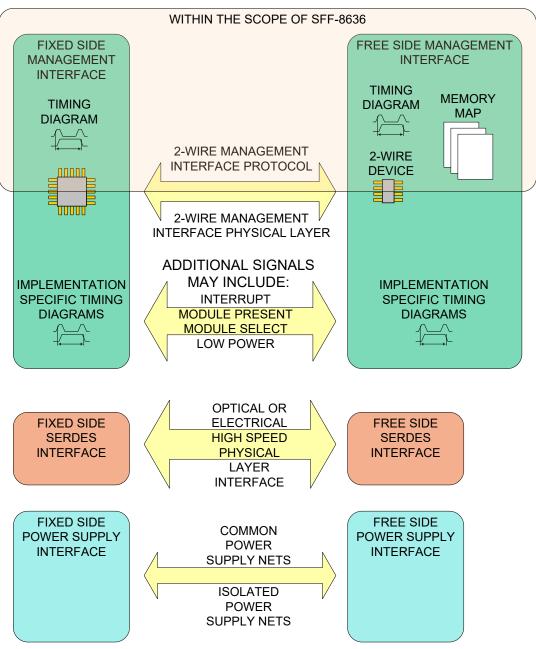

# 4.1 Fixed-to-Free Side Block Diagram

Note, in Figure 4-1, the limitations in the scope of SFF-8636 to the fixed-to-free side management interface.

Figure 4-1 Common Management Interface Block Diagram

# 4.2 Signal Definition

The 2-wire management interface includes the following signals.

### 4.2.1 SCL

2-wire interface clock.

#### 4.2.2 SDA

2-wire interface data.

## 4.2.3 Other Signals

Additional signals such as power, module present, interrupt, reset, and low-power mode may be implemented but are beyond the scope of SFF-8636. Refer to the relevant hardware specification for information on these signals.

# 4.3 Physical Implementation

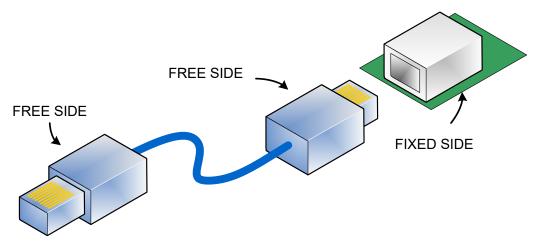

## 4.3.1 Cable Assembly

The interconnect implementation may be a passive or active copper cable assembly or an active optical cable assembly, as illustrated in Figure 4-2.

Figure 4-2 Cable Assembly Implementation

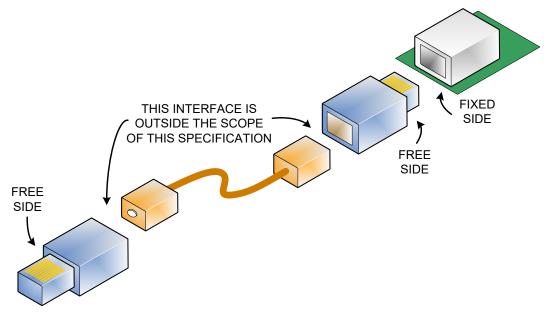

## 4.3.2 Separable Transceiver Modules

Figure 4-3 depicts a separable active copper or optical transceiver interconnect implementation. Only the management interface between the fixed and free side is within the scope of this document.

Figure 4-3 Separable Transceiver Module Implementation

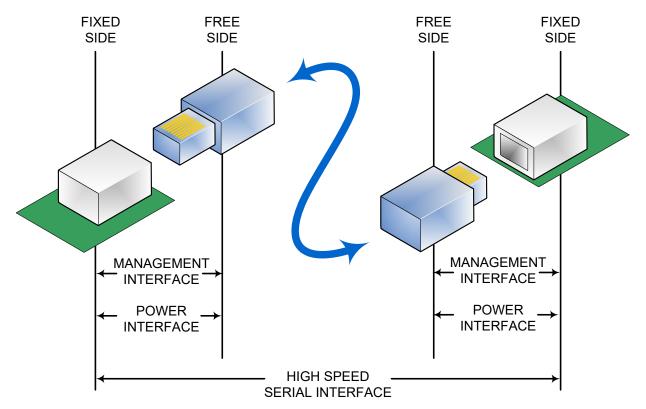

## 4.3.3 Management Interface Scope

The scope of the management and active cable power interfaces is limited. Note that management and power interfaces do not extend from one free side end of the cable to the other.

**Figure 4-4 Management Interface Scope**

### 4.4 Reset Behavior

#### 4.4.1 Protocol Reset

Synchronization issues may cause the controller and target state machines to disagree on the specific bit location currently being transferred. See 5.2.2.

#### 4.4.2 Power On Reset

When power is applied, the module will set all registers to their default values and reset the 2-wire interface. The timing is specified in the relevant hardware specification.

## 4.4.3 Reset Signals

Some implementations may include a reset pin (ResetL) and/or the optional software reset bit (see Page 00h Byte 93 bit 7). If provided, upon assertion of either signal the module will set all registers to their default values and reset the 2-wire interface. The timing is specified in the relevant hardware specification.

# 5 2-wire Bus Interface

## 5.1 Signal Interface

The 2-wire interface shall consist of a controller and a target. The fixed side shall be the controller and the free side shall be the target. Control and data are transferred serially. The controller shall initiate all data transfers. Data can be transferred from the controller to the target and from the target to the controller. The 2-wire interface shall consist of the clock (SCL) and data (SDA) signals.

The controller utilizes SCL to clock data and control information on the 2-wire bus. The controller and target shall latch the state of SDA on the positive transitioning edge of SCL.

The SDA signal is bi-directional. During data transfer, the SDA signal shall transition when SCL is low. A transition on the SDA signal, while SCL is high, shall indicate a stop or start condition.

#### 5.2 2-wire Bus Protocol

### **5.2.1** The operational States and State Transitions

#### 5.2.1.1 Start

A high-to-low transition of SDA with SCL high is a START condition. All 2-wire bus operations shall begin with a START condition.

#### 5.2.1.2 Stop

A low-to-high transition of SDA with SCL high is a STOP condition. All 2-wire bus operations shall end with a STOP condition

#### 5.2.1.3 Acknowledge

After sending each 8-bit word, the side driving the 2-wire bus releases the SDA line for one-bit time, during which the monitoring side of the 2-wire bus is allowed to pull SDA low (zero) to acknowledge (ACK) that it has received each word. Write data operations shall be acknowledged by the target for all bytes. Read data operations shall be acknowledged by the controller for all but the final byte read, for which the controller shall respond with a non-acknowledge (NACK) by permitting SDA to remain high and followed by a STOP.

#### 5.2.1.4 Clock Stretching

To extend the transfer the target asserts clock low. This can be used by the target to delay completion of the operation.

#### 5.2.2 Protocol Reset

Synchronization issues may cause the controller and target state machines to disagree on the specific bit location currently being transferred, the type of operation or even if an operation is in progress. The 2-wire interface protocol has no explicitly defined reset mechanism. The following procedure may force completion of the current operation and cause the target to release SDA.

- a) The controller shall provide up to nine SCL clock cycles (drive low, then high) to the target.

- b) The controller shall monitor SDA while SCL is high on each cycle.

- c) If the target releases SDA, it will be high and the controller shall initiate a START condition.

- d) If SDA remains low after a full nine clock cycles the protocol reset has failed.

#### **5.2.3 Format**

#### 5.2.3.1 Control

After the start condition, the first 8-bit word of a 2-wire bus operation shall consist of the 7-bit target address '1010000' followed by a read/write control bit.

| 1   | 0 | 1 | 0 | 0 | 0 | 0 | R/W |

|-----|---|---|---|---|---|---|-----|

| MSB |   |   |   |   |   |   | LSB |

The least significant bit indicates if the operation is a data read or write. A read operation is performed if this bit is high and a write operation is executed if this bit is set low. Upon completion of the control word transmission, the target shall assert the SDA signal low to acknowledge delivery (ACK) of the control/address word.

#### 5.2.3.2 Address and Data

Following the read/write control bit, and acknowledgment by the target, addresses and data words are transmitted in 8-bit words with the most significant bit (MSB) first.

### 5.3 Read/Write Operations

## **5.3.1 Target Memory Address Counter (Read and Write Operations)**

All 2-wire targets maintain an internal data word address counter containing the address accessed by the latest read or write operation, incremented by one. The address counter is incremented whenever a data word is received or sent by the target. This address remains valid between operations as long as the power to the target is maintained. Upon loss of power to or reset of the free side device, the target address counter contents may be indeterminate. The address rolls over from the last byte of the 128-byte memory page to the first byte of the same page.

### **5.3.2 Write Operations (BYTE Write)**